良い観察です。

この「2直列×2並列の抵抗アレイ」は、現場でもよく見かける構成で、

典型的には以下3つのどれかの目的で使われています。

順に、構造 → 電気的効果 → 設計上の狙いをわかりやすく説明します。

目次

🧩 まず構造のイメージ

┌─R1─R2─┐

信号 ─┤ ├──→ 次段(2.2kなどへ)

└─R3─R4─┘

- 「R1–R2」 が1本の直列ペア

- 「R3–R4」 がもう1本の直列ペア

- それを 並列 にしている形

→ つまり 4つの抵抗で構成された T型ではない、単純な“対称2直2並列”。

⚙️ 主な3つの用途(回路目的)

| 用途 | 内容・目的 | 現場での代表例 |

|---|---|---|

| ① ノイズ吸収・ライン保護用の分散抵抗 | 瞬間的なESD/サージが来たときに、抵抗1本あたりの負担を減らす。抵抗1本あたりの電圧降下を半分にし、静電耐量を上げる。 | コネクタ直後の信号ライン(外部入力保護) |

| ② 精度向上(抵抗値微調整) | 抵抗値を分割して構成し、トータル抵抗値を設計値に合わせやすくする。例えば2.2 kΩが在庫にない場合に、2 × 4.4 kΩ 並列で実現など。 | 高精度アナログライン(分圧・基準電圧生成) |

| ③ 熱分散・信頼性向上 | 大きな電力を1本で流すと熱ストレスが集中するため、2本並列で半分ずつ分担。高温・連続運転回路で安定化できる。 | 電源ラインのドロップ抵抗や電流制限抵抗など |

パルス/ESDの電力分散(各枝で電流が半分)

各抵抗の印加電圧が半分 → サージ耐量↑

在庫/実装の都合で値を作りやすい

が主な狙いです。

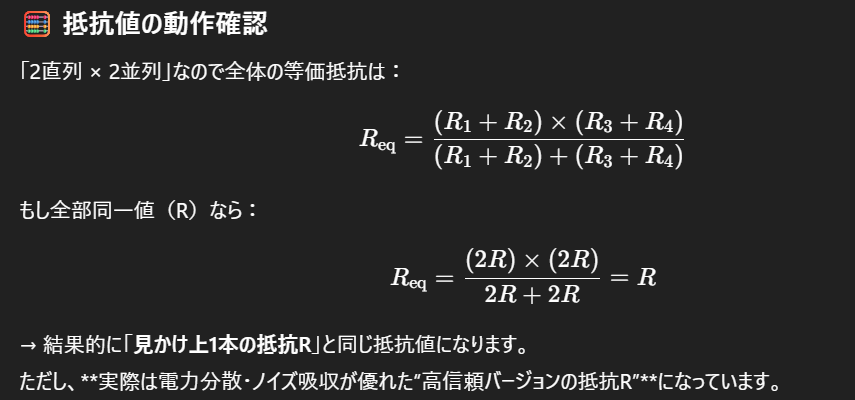

🧮 抵抗値の動作確認

🧠 回路的な意味合い(今回の位置関係から)

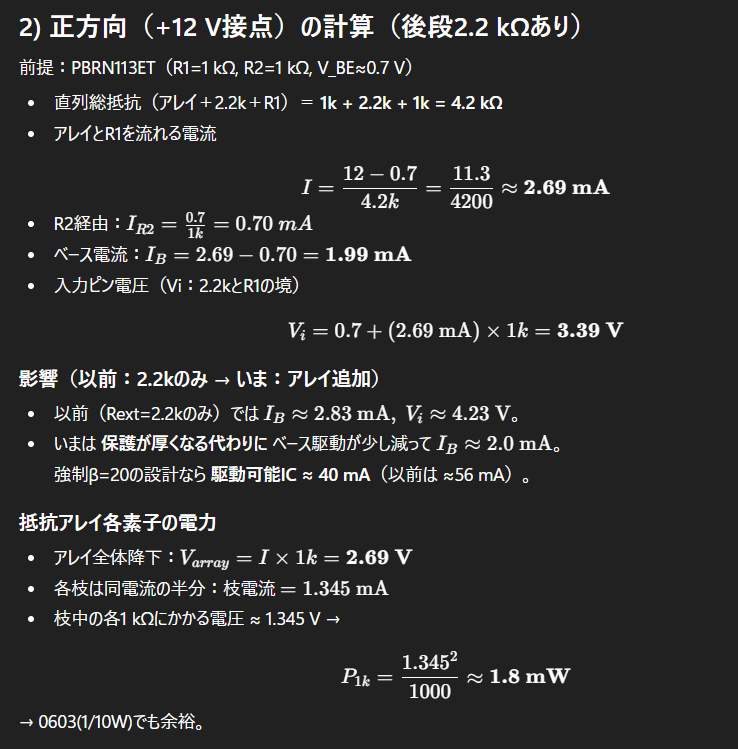

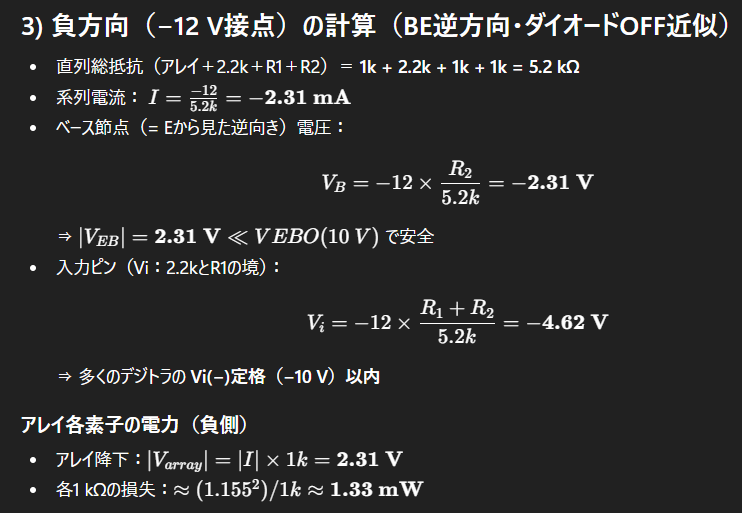

「2.2 kΩの前段にある」=外部コネクタ → この抵抗アレイ → 2.2 kΩ → デジタルトランジスタベース

この場合の役割はほぼ確実に:

✅ 「外部入力保護・ノイズフィルタ兼 電流制限の前段分散抵抗」

詳しく言うと:

- コネクタから外来サージ・ESDが入る

- まずこの 2直2並列抵抗 で

- インパルス電流を分散

- 瞬間電圧を分割

- 抵抗体1本あたりの過渡エネルギーを軽減

- その後ろの 2.2 kΩ が

- 定常時のベース電流制限

- 回路内への突入電流防止

つまり、

⚡「外部ノイズ → 分散抵抗で和らげる → 2.2kで制限 → トランジスタで受ける」

という多段防御フィルタ兼リミッタです。

📈 参考:等価的に見ると

回路全体はこうなります。

(外部入力)

│

┌─┬─┐

│R│R│ ← 並列ブランチ(2直2並列構成)

└─┴─┘

│

2.2kΩ ← 入力制限

│

B端子(デジトラ)

これを高周波的に見ると:

- 分散抵抗がESDや高周波ノイズを一次で吸収

- 2.2kが低周波~定常信号の制限

- 必要に応じて並列にコンデンサ(C)を追加してRCローパスにすることもあります。

🔍 推測の根拠(業界的に)

| 観点 | 備考 |

|---|---|

| 配置が「コネクタ直後」 | ESD・サージ・ノイズ対策位置 |

| 値が等しい4本構成 | 分散目的である可能性高い |

| 後段に2.2k | 本命は電流制限、前段は保護階層 |

| トランジスタ入力 | 高インピーダンス → フィルタやESD保護を入れやすい |

✅ 結論(実務的まとめ)

| 目的 | 内容 |

|---|---|

| 主目的 | 外部入力信号のESD・ノイズ緩和+電流分散 |

| 副次効果 | 抵抗精度UP、温度分散(抵抗1本あたりの熱負担を低減) |

| 等価抵抗 | 各抵抗が同値なら合成値は単体と同じ |

| 設計ポイント | 各抵抗の定格電力を半分に見積もれる(2並列のため) |

| 類似構成 | ノイズラインの「分割抵抗」「多段ESD吸収抵抗」など |