本記事ではデジタルトランジスタのデータシートに記載されている用語についての解説と、各種パラメータを利用した設計計算方法について解説しております。デジタルトランジスタは基本的にスイッチング用途で使用しますのでその前提で設計を行います。

絶対最大定格(壊さないための上限)

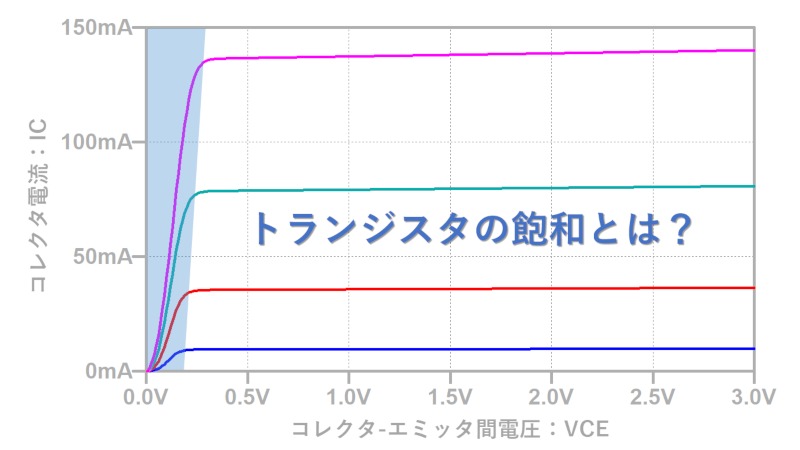

IC-hFE特性

任意のコレクタ電流値での直流電流増幅率hfeの値をグラフ化したものです。任意のコレクタ電流を流す場合に必要なベース電流Ibの値を求めるために使用します。

例)流したいコレクタ電流Ic=5mAの時、下記グラフより電流増幅率hfe=8、よってコレクタ電流Ic=5mA流すのに必要なベース電流Ib=Ic/hfe=0.625mAとなる。

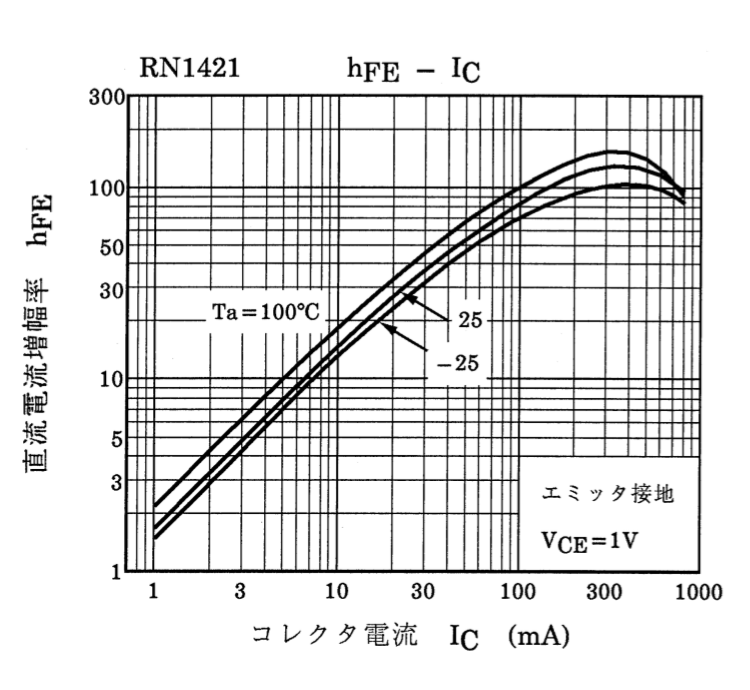

Ic-Vi(on)特性

任意のコレクタ電流値でのオン電圧Vi(on)の値をグラフ化したものです。このグラフで読み取った値にデータシート内の電気的特性と特性グラフを比較して出した部品ばらつきを加算した値が部品ばらつきを考慮したオン電圧となる。

例)コレクタ電流Ic=5mAの時、下記グラフよりオン電圧Vi(on)=1.5V、データシートの電気的特性よりIc=100mA、VCE=0.2Vの時オン電圧Vi(on)=3.5V、下記グラフの同条件時のオン電圧は2.5Vのため部品ばらつきが+1.0Vあると考えられる。よって部品ばらつきを考慮したオン電圧Vi(on)=1.5+1.0=2.5Vとなる。

絶対最大定格はどの値に関しても瞬間的でも超えてはならない上限値になります。

これを超えると破壊や損傷および劣化の原因となり、破裂・燃焼による障害を負うことがあります。

VCBO(コレクタ–ベース耐圧、開放エミッタ)

エミッタ開放時(トランジスタOFF時)にコレクタ-ベース間に逆方向(コレクタ:+、ベース:-)の電圧を印加した際に耐えうる最大電圧です。こちらはトランジスタの理論的OFF時耐圧になります。実際のOFF耐圧はVCEOを使用しましょう。

| 項目 | 内容 |

|---|---|

| 定義 | エミッタを開放した状態で、コレクタ–ベース間に逆電圧を印加したときに壊れない最大電圧。 |

| 一般的な値 | 約 40〜60 V(PBRN113ET は 40 V) |

| 問題になるとき | コレクタが電源側で高電圧に引っ張られるとき(トランジスタ OFF 時)。 |

| 具体的な例 | ・リレーやモータ駆動回路のスイッチオフ時に発生する誘導サージ・外部ノイズや雷サージでコレクタに過電圧が加わる・ベースがオープンのまま出力ノードが浮いて高電圧を受ける |

| 超えるとどうなるか | ベース–コレクタ接合がアバランシェ破壊し、リーク増加・素子短絡・最悪焼損。 |

| 考慮する場面 | 出力段(オープンコレクタ出力・センサドライバ・トランジスタスイッチなど)。 |

| 主な対策 | ・コレクタ–電源間にツェナーダイオードまたは TVS でクランプ・誘導負荷の場合はフライホイールダイオード・ベースを確実に抵抗でプルダウンして浮かせない |

| 覚え方 | 👉 「出力側(コレクタ)にプラス方向の過電圧が来るときに注意」 |

イメージがわかない方にトランジスタの通常動作時の各端子の電位関係とVCBOの時の電位関係を記載します。

これを見るとトランジスタOFF時もVCBOと同じ電位関係です。ただし、VCBOはサージなどでコレクタ電位が高い場合を想定しています。

| 状態 | ベース | コレクタ | 接合状態 | 説明 |

|---|---|---|---|---|

| 通常ON | 約0.7 V | 約0.2 V | 順方向 | ベース–エミッタ間に電流が流れ、C–E導通 |

| 通常OFF(スイッチOFF) | 0 V | +3.3 V | 逆方向 | コレクタ高電位、ベース低電位(=VCBO測定状態と同じ) |

| VCBO測定時 | 0 V(またはGND) | 高電圧(例: +40 V) | 逆方向 | 耐圧試験の条件。エミッタ開放でB–C接合を逆バイアスする |

VCEO(コレクタ–エミッタ耐圧、開放ベース)

トランジスタOFF時のコレクタ-エミッタ間の耐圧。通常のスイッチ動作(ベース制御)ではオフ時のVCEがこの値を超えないこと。通常使用時は電源電圧(例:3.3Vや5V)でしか動かさないが、

外来ノイズ・誘導サージで一瞬高電圧が掛かる可能性があるため、VCEOが重要になります。

| 状態 | 電圧の方向 | 実際の意味 |

|---|---|---|

| 通常ON | コレクタ → エミッタ(順方向) | スイッチON、VCE(sat)の世界 |

| 通常OFF | コレクタ → エミッタ(逆方向) | 出力がHIGH、VCE ≈ 電源電圧 |

| VCEO定義 | コレクタ → エミッタ(逆方向、ベース開放) | OFF時に印加できる最大耐圧(例:40 V) |

発生メカニズムは以下のようになります。実際のOFF状態でベースが完全固定ではなく“浮いている”場合に近く、特にベースプルダウン抵抗が弱い(高抵抗)と、この状態に近づくためVCEOは実際の回路耐圧に近い定格値です。

- コレクタ–ベース間が逆方向バイアスされます(C+、B−)。

- しかしベースが開放のため、B–C接合で発生する逆リーク電流がベースの電位を変化させます。

- この電流がさらにベース–エミッタ接合を順方向にわずかにバイアスしてしまうのです。

- C–B で発生したリーク → B–E へ流れる → E–B間の順方向電流増加 → avalancheが連鎖して破壊が早まる

というメカニズムで、

VCEO は VCBO より低くなるのです。

VEBO(エミッタ–ベース耐圧、開放コレクタ)

コレクタ解放時にベース-エミッタ間に逆方向(ベース:-、エミッタ+)の電圧を印加した際に耐えうる最大電圧です。

| 項目 | 内容 |

|---|---|

| 定義 | コレクタを開放した状態で、ベース–エミッタ間に逆電圧を印加したときに壊れない最大電圧。 |

| 一般的な値 | 約 5〜10 V(PBRN113ET は 10 V) |

| 問題になるとき | ベース端子が GND よりマイナス側になるとき(負電圧) |

| 具体的な例 | ・外部センサからの信号が −数V 振れる・GND レベルのズレでベース側がマイナスになる・コネクタから静電気が入る・入力が開放されて外乱ノイズを拾う |

| 超えるとどうなるか | ベース–エミッタ接合が逆方向にアバランシェ破壊し、hFE 低下・リーク電流増大・最悪破損。 |

| 考慮する場面 | 外部入力を受けるトランジスタ(センサ入力や信号インターフェースなど)。 |

| 主な対策 | ・ベース直列抵抗(Rin)で電流制限・ベース–エミッタ間にダイオードを入れて負電圧をクランプ・コネクタに TVS ダイオードを配置 |

| 覚え方 | 👉 「入力側(ベース)にマイナス電圧が来るときに注意」 |

メカニズムとしては以下になります。

- BE接合がアバランシェ破壊し、局所的に高電流が流れる

- 数回の過電圧で hFE(増幅率)低下/リーク電流増大

- 最悪、**BE間短絡(内部ショート)**が起きる

- この破壊は一度でも起きると不可逆(元に戻らない)

VEBOを考慮するべき場面です。

| 想定される状況 | 発生原因 | 対策・設計上のポイント |

|---|---|---|

| ① 外部信号が負電圧になる | 圧力センサなどが他電源系と接続され、GND電位差でベースがマイナス側へ振れる | ベース入力に**直列抵抗(Rin)**を入れて電流制限。 |

| ② コネクタからの静電気(ESD) | 人体帯電でベースピンに ± 数kVのスパイク | TVSダイオードや保護抵抗でクランプ。 |

| ③ オープン入力(浮遊時のノイズ) | ベースがプルダウンされていないと、外乱で負側電圧が一瞬発生 | B–E間に保護ダイオードを入れる。 |

| ④ 電源OFF時の電位差 | 電源の立上げ・立下げタイミングでベース電位だけ残る | 電源シーケンスを整える/ダイオードでクランプ。 |

そのため以下のように設計を行いましょう。

| 設計目的 | VEBOの使い方 | 設計方針 |

|---|---|---|

| 入力回路の保護設計 | “逆電圧がこれを超えないことを確認” | コネクタからの負電圧・ESD電圧を評価し、TVS/ダイオード/抵抗で制限する。 |

| マイコン入力などの信号整合 | “入力信号レンジが−0.3 V 〜 (VDD+0.3 V)”以内になるよう設計 | ベース–エミッタ逆電圧を確実に抑える。 |

| 静電気・雷サージ試験 | “瞬間的に VEBOを超えないよう保護素子を配置” | TVSまたはクランプダイオードで制限。 |

| 基板レイアウト | “ベースパターンをGND近くに置かない” | 大電流GNDループによる逆電圧誘導を防止。 |

VI(+)/Vi(-)(正負入力電圧)

デジタルトランジスタに入力できる電圧の許容値の目安になります。

ここでいう「入力電圧(Vi)」とは、 デジトラの入力ピン(内部R1の手前)に実際に現れる電圧です。

あくまで目安のため、実際はトランジスタの損失を確認し、熱破壊に至らないかを確認すること。

計算にて実際に入力されるViの値を求めることが出来ます。2.2Kの外付け抵抗を接続したときで考えてみましょう。

Vi(+)の場合

まずは外付け抵抗Rext及びR1に流れてくる電流を求めましょう。(外付け抵抗が無い時はRextは0Ωで考えましょう)

トランジスタがONしていると考えることが出来るのでベース・エミッタ間電圧VBE≒0.7Vを加味して、印加電圧Vから引く。

IRext=\(\frac{V-VBE}{Rext+R1}\)

例として印加電圧Vが12V、外付け抵抗Rextが2.2KΩ、内臓抵抗R1が1kΩの場合で考える

IRext=\(\frac{12-0.7}{2.2k+1.0k}\)=3.53mA

次に内臓抵抗R2に流れる電流も求める。R2に掛かる電圧はベース・エミッタ間と並列に接続されているためVBEと同電位になる。

IR2=\(\frac{VBE}{R2} \)

例としてベース・エミッタ間電圧VBEが0.7V、内臓抵抗R2が1kΩの場合で考える

IR2=\(\frac{0.7}{1.0k} \)=0.7mA

よってトランジスタのベース電流IBは外付け抵抗とR1に流れる電流からR2に分流する電流を引いた値になる。

IB=IRext-IR2

例として先ほど求めたIRextとIR2により、ベース電流IBは以下となる。

IB=IRext-IR2=3.53-0.7=2.83mA

最後に正入力電圧Vi+を求めます。Vi+はベース・エミッタ間電圧VBEとR1で発生する電圧降下の合計分あるはずなので以下の式になります。

Vi+=VBE+(IRext×R1)

例としてベース・エミッタ間電圧VBEが0.7V、内臓抵抗R1が1kΩ、R1に流れる電流IRext=3.53mAの場合で考える

Vi+=0.7+(3.53m×1.0k)=0.7+3.53=4.23V

よって以下のように判断することが出来る

- データシートの Vi(+) = +10 V 定格を大きく下回る安全な値。

- 入力電流も約3.5 mAと適正範囲。

- 飽和駆動としても十分な電流を確保。

| 項目 | 計算値 | 備考 |

|---|---|---|

| 外付け抵抗電流 (I_{Rext}) | 3.53 mA | 12 V → 内部入力へ流入 |

| 内部入力電圧 (V_i) | 約 4.2 V | デジトラの入力ピン電位(安全域) |

| ベース電流 (I_B) | 2.8 mA | 飽和駆動十分(β_forced=20でIC≈56 mA駆動可能) |

| 損失(R1+Rext) | (3.53 mA)²×3.2 kΩ≈40 mW | 余裕あり |

| Vi(+)定格との比較 | +4.2 V ≪ +10 V | 安全動作範囲内 |

| 項目 | 式 | 結果 | コメント |

|---|---|---|---|

| 入力電流 (I_{IN}) | (12 V−0.7 V)/(Rext+R1)=3.53 mA | OK | 外部電流制限OK |

| 入力電圧 (V_i) | 0.7 V+I_R×R1=4.23 V | OK | 定格±10 V内 |

| ベース電流 (I_B) | 2.83 mA | OK | IC≈β_forced×IB=約56 mA可能 |

| 損失 (P_{sum}) | (3.53 mA)²×(R1+Rext)=40 mW | OK | 熱的に余裕あり |

Vi(-)の場合

負入力の場合はトランジスタOFFのため、直列接続のRext・R1・R2の分圧+直列電流で求めることが出来ます。

(外付け抵抗が無い時はRextは0Ωで考えましょう)

まずは合成直列抵抗を求めましょう。以下のように求めます。

RΣ=Rext+R1+R2

例として外付け抵抗Rextが2.2kΩ、内臓抵抗R1及びR2が1.0kΩで考えると、

RΣ=2.2+1.0+1.0=4.2kΩ

次にこれらの抵抗に負入力電圧Vを入力した場合に流れる電流を求めます。

IΣ=\(\ frac{V}{RΣ}\)

例として負電圧Vがー12V、合成抵抗RΣが4.2kΩで考えると

IΣ=\(\ frac{-12}{4.2k}\)=2.857mA

次にエミッタ・ベース間に掛かる電圧VEBを求めましょう。これは負入力電圧Vを直列合成抵抗RΣに対する内臓抵抗R2の分圧により、求めることが出来ます。

VEB=\(\ V×\frac{R2}{RΣ}\)

例として負入力電圧Vが-12V、内臓抵抗R2が1.0kΩ、直列合成抵抗RΣが4.2kΩとすると

VEB=\(\ -12×\frac{1.0k}{4.2k}\)=-2.857V

最後に負入力電圧Vi-を求めます。Vi-はこれは負入力電圧Vを直列合成抵抗RΣに対する内臓抵抗R1とR2の合成抵抗による分圧にて求めることが出来ます。

Vi-=\(\ V×\frac{R1+R2}{RΣ}\)

例として内臓抵抗R1とR2が1.0kΩ、負入力電圧Vが-12V、合成抵抗RΣが4.2kΩとして考えると、

Vi-=\(\ -12×\frac{1.0k+1.0k}{4.2k}\)=-5.714V

よって以下のように判断することが出来る。この条件なら安全に使用することが可能と判断できる。

- |VEB|=2.857V<VEBO(=10V)であり、逆方向破壊無し

- Vi-=-5.714<Vi(-)=-10Vで定格以内であるため、問題なし。

Vi-がデータシートに記載がない場合

Vi±がデータシートに無い場合でも、BE逆耐圧(VEBO)で安全判定ができます。

上記の計算で|VEB|とVEBOを比較して確認できれば問題ないことは確認OK

IO(出力電流=コレクタ電流IC 連続)

熱と飽和電圧により上限下がる。活性領域で動作しているときのコレクタ電流の最大値であり、飽和を深く(hFeを低く)した場合、R1で消費される電力が1/8Wを超えやすくなってしまう。

IO(出力電流=コレクタ電流 連続):最大 600 mA(実装フットプリント標準時)。拡張パッド(コレクタ 1 cm²)で 700 mA(注記 [2])。熱と飽和電圧で実効上限はさらに下がるため熱設計とVCE(sat)確認が必須。(Nexperia Assets)

IO(出力電流=連続コレクタ電流)

目的:熱条件を含めた連続許容電流。基板条件で値が変わる(標準フットプリントとコレクタ1 cm²パッドで差)。

設計読み:VCE(sat)による損失P≈IC·VCE(sat)と、後述Rθを使った温度上昇ΔTjで同時にチェック。(Nexperia Assets)

IORM(繰返しピーク出力電流)

想定パルスがデータシート記載のtp:パルス幅やδ:デューティー比に収まっているかをまず確認。

収まっていればパルス電流による熱損失を計算し、問題ないことを確認しましょう。

まず、tp:パルス幅やδ:デューティー比ですが、例:tp≤1 ms, δ≤0.33であればこの値に収まっている必要があります。δは以下のように求めることが出来ます。

δ=tp/T=tp×f

※T:パルス周期

※f:パルス周波数

上記が条件内であれば以下の式で損失熱を計算します。

P=Icp×VCE(sat)

※Icp:パルス電流

※VCE(sat):トランジスタON時のVCE間電圧

IORMの記載がデータシートにない場合

IORMがデータシート内に記載がない場合は、平均損失やパルス瞬時温度上昇により、判断することが出来る。

以下に計算方法を示す。

①平均損失

パルスによる平均損失により、 問題ないかを判断する方法を説明する。

Pavg=ICpeak・VCE(sat)・δ

例としてパルスピーク電流ICpeak=200mA、パルス幅tp=1.0ms、繰り返し周波数100Hz(デューティー比δ=0.1)、

IB=10mA、VCE(sat)=85mV(IC=200mA,IB=10mA条件時の最大電圧をデータシートより採用)の時は

Pavg=0.2A×0.085V×0.1=1.7mW

上記より、パルスによる熱損失を求めれたので、次に許容できる損失量を求める。

Pmax=(Tj-Tamb)/Rth(j-a)

例として、ジャンクション温度Tj=150℃、環境温度Tamb=60℃、ジャンクション-周囲間熱抵抗Rth(j-a)=500K/Wとすると

Pmax=(150-60)/500=180mW

上記により、許容損失180mWに対し、パルスによる損失は1.7mWのため、問題なし、OK

➁パルス瞬時温度上昇

過渡熱インピーダンスZth(j-a)を特性グラフから確認し、問題ないかを判断する方法を説明する

Ppeak=ICpeak×VCE(sat)

例として、パルスピーク電流ICpeak=200mA、、VCE(sat)=85mV(IC=200mA,IB=10mA条件時の最大電圧をデータシートより採用)の時は

Ppeak=0.2×0.085=17mW

次に上記で求めた損失により、温度上昇がどれほど発生するかを確認する。

ΔTj=Ppeak×Zth(j-a)

例としてZth(j-a)=30K/W(データシート内の特性グラフより、tp=1ms、δ=0.1の時の値を採用)、Ppeak=17mWの時として考えると

ΔTj=0.017W×30K/W=0.51℃

上記を環境温度Tabm=60℃に合計した場合でもジャンクション温度Tj=150℃に収まっていればOK

Ptot(総損失)

デジタルトランジスタの損失はコレクタ・エミッタ間損失に加えて内部抵抗R1・R2による損失やベース・エミッタ間損失も含めた4つの損失の合計になります。

総損失は以下のように求めることが出来ます。

Ptot=PR1+PR2+Pce+Peb

※PR1:内臓抵抗R1による損失

※PR2:内臓抵抗R2による損失

※Pce:コレクタエミッタ間による損失

※Peb:ベースエミッタ間による損失

それぞれの損失を式に変換すると

Ptot=\(\ (VBE×IR1)+(VBE×IR2)+(VCE×IC)+(VBE×IB)\)

※VBE:ベース・エミッタ間電圧

※IR1:内臓抵抗R1に流れる電流

※IR2:内臓抵抗R2に流れる電流

※VCE:コレクタエミッタ間飽和電圧

※IC:コレクタ電流

※IB:ベース電流

Tj(接合温度)/Tamb(周囲温度)/Tstg(保存温度)

Tj(接合温度):150 °C(最大)/Tamb(周囲温度):−65 ~ +150 °C/Tstg(保存温度):−65 ~ +150 °C

絶対最大であり、連続運用はより低い温度域に制限すべき(IEC 60134の定義に準拠と明記)。(Nexperia Assets)

Tj / Tamb / Tstg(接合・周囲・保存温度)

目的:動作・保管の温度限界。

設計読み:Tj(max)=150 °Cを超えないよう、P×Rθ(j-a)+Tambで見積もり。(Nexperia Assets)

熱特性

熱特性に関しては下記の記事を参考にしてください

Rθ(j-a)(接合–周囲 熱抵抗)

接合–周囲 熱抵抗。基板の配銅・パッド面積に大きく依存。

素子接合から周囲空気までの温度上昇係数[K/W]。基板条件で大きく変化

Rθ(j-sp)(接合–はんだ点 熱抵抗)

接合→はんだ点 熱抵抗

パッケージから基板へ熱が抜ける局所経路の指標。

Zθ(j-a)(過渡熱インピーダンス)

パルス幅とデューティに依存する時定数特性。短パルス駆動時の一時的な許容損失計算に使用(図2/図3 を参照)。

パルス幅・デューティで一時的に小さくなる見かけのRθ。

設計読み:IORMなど短パルスの温度上昇は**ΔTj(t)≈∑Pi·Zθ(t)**で評価。特性グラフ曲線を使用。

電気的特性(使える範囲の目安)

V(BR)CBO:コレクタ・ベース間電圧

あくまで補助的な値

V(BR)CEO:コレクタ・エミッタ間電圧

トランジスタOFF時にC-E間に掛けても良い現実的な最大電圧。

これが電源電圧+サージ電圧よりも大きいことを確認しましょう。

ICBO(コレクタ–ベース漏れ)

エミッタオープンでコレクタ・ベース間に逆バイアス(コレクタ:+、ベース:ー)を定格まで印加した際のリーク電流の最大値

ICEO(コレクタ–エミッタ漏れ)

ベースオープンでコレクタ・エミッタ間に定格電圧印加(コレクタ:+、エミッタ:ー)した際のリーク電流の最大値

IEBO(エミッタ–ベース漏れ)

コレクタオープンでベース・エミッタ間に逆バイアス(エミッタ:+、ベース:-)を定格まで印加した際のリーク電流の最大値。

抵抗比 R1/R2 の大きな製品ほど電流は大きくなり、また同時に抵抗R2に電流IR2が流れるため、

同一抵抗比の場合、R1 の大きな製品ほど小さくなります。

異なるIEBOの計測条件の部品のスペック比較方法

部品のスペックを比較したときに片方の部品は|VEB|=5Vの時にIEBO=4mA、もう片方の部品は|VEB|=10Vの時にIEBO=7.25mAなどと記載されている場合、|VEB|条件が違うため、一目で優劣比較はできません。

この場合は、上記の値を条件値として考え、実際にかかる|VEB|を求めて、その値が上記の|VEB|条件より、下回っている電圧であれば上記のIEBO以下までしか流れないことが分かるのでそのような判断をしましょう。

まずは、実際の回路での|VEB|を求めましょう。計算方法は

負入力の場合はトランジスタOFFのため、直列接続のRext・R1・R2の分圧+直列電流で求めることが出来ます。

(外付け抵抗が無い時はRextは0Ωで考えましょう)

まずは合成直列抵抗を求めましょう。以下のように求めます。

RΣ=Rext+R1+R2

例として外付け抵抗Rextが2.2kΩ、内臓抵抗R1及びR2が1.0kΩで考えると、

RΣ=2.2+1.0+1.0=4.2kΩ

次にこれらの抵抗に負入力電圧Vを入力した場合に流れる電流を求めます。

IΣ=\(\ frac{V}{RΣ}\)

例として負電圧Vがー12V、合成抵抗RΣが4.2kΩで考えると

IΣ=\(\ frac{-12}{4.2k}\)=-2.857mA

次にエミッタ・ベース間に掛かる電圧VEBを求めましょう。これは負入力電圧Vを直列合成抵抗RΣに対する内臓抵抗R2の分圧により、求めることが出来ます。

VEB=\(\ V×\frac{R2}{RΣ}\)

例として負入力電圧Vが-12V、内臓抵抗R2が1.0kΩ、直列合成抵抗RΣが4.2kΩとすると

VEB=\(\ -12×\frac{1.0k}{4.2k}\)=-2.857V

上記により、実際の回路に掛かるVEBは-2.857Vまでであり、データシート内での条件|VEB|=5V及び|VEB|=10V

よりも低いため、IEBO=4mA、IEBO=7.25mAよりも低い電流が流れることが分かる。

これにより、判断することが出来る。

hFE(直流電流増幅率)

トランジスタが活性領域(増幅率の上昇が無くなった時)の直流電流増幅率になります。

スイッチング用途の場合は飽和領域(増幅率が上昇しているとき)の増幅率を参照しますので、

この値は使用しません。VCE(sat)表で損失を見て、増幅率を仮定して計算していきます。

VCE(sat)(コレクタ–エミッタ飽和電圧)

トランジスタオン時に残るC-E間電圧。IBを増やす/温度を下げると低下、ICを増やすと上昇する。

この電圧とコレクタ電流による熱損失が実質トランジスタの熱損失の大半となる。

VI(on)(オン側入力電圧):

Vi(on) は “所定のIC(ここでは20 mA)・所定のVCE(0.3 V)を満たすために必要な最小入力”の境界。

つまりしっかりとVCEが飽和するコレクタ電流が流れるだけの入力電圧の目安です。

設計ではVi(on)の最大値以上の入力電圧に回路ON時になるようにしましょう。設計手順は以下になります。

①必要なコレクタ電流ICを決める

所定のVCE(sat)の値になるコレクタ電流に特性グラフから読み取る。

➁強制βを設定する

強制βはトランジスタが確実にONするために低めに見積もった増幅率のこと。中途半端にトランジスタがONした状態だとVCE(sat)が大きくなるため、熱損失が増大するためである。

| 設計目的 | 強制βの目安 | 理由 |

|---|---|---|

| 小信号スイッチ(数mA) | 50〜100 | 飽和させるためのマージン確保 |

| 一般スイッチング(10〜100 mA) | 10〜50 | h_FEのばらつき・温度変動対策 |

| パワー段(リレー駆動など) | 5〜20 | 確実な飽和(VCEsat低減) |

③上記①➁で設定した値から必要なベース電流IBを求める。

上記により設定したコレクタ電流値と強制βを用いて必要なベース電流値を計算しましょう。

以下の計算で求めることが出来ます。

IB=IC/β

④上記③にて求めたベース電流にてトランジスタをONするために必要な最低入力電圧を求める

上記により求めたベース電流値と内臓抵抗R1・R2とベース・エミッタ間電圧VBEを用いて、

トランジスタを完全にONにするために必要な入力電圧値を求めましょう。計算は下記になります。

Vi=\(\ VBE(1+\frac{R1}{R2})+R1・IB\)

上記で求めた入力電圧値が入力電圧定格Vi±以内に収まっているかを確認しながら入力電圧を調整しましょう。

VI(off)(オフ側入力電圧)

トランジスタが確実にOFFになる入力電圧の範囲になります。設計ではVi(off)の最大値以下の入力電圧になるように

回路OFF時の電圧がなっているように設計しましょう。

R1(バイアス抵抗1)

Cc(コレクタ容量):

Cc(コレクタ容量):typ 7 pF(VCB=10 V, f=1 MHz)

→ 立上り/立下りやEMCに影響。高インピーダンス負荷や高速エッジではスルーレートに効く指標。(Nexperia Assets)

Cc(コレクタ容量)

目的:C-B接合由来の容量。高速エッジでスルーレートやリンギング、EMIに影響。

設計読み:ハイインピーダンス負荷や数十MHz以上の信号では、立上り遅れやクロストーク要因になるため、配線容量と併せて見積もる。(Nexperia Assets)

参考文献

まとめ

本記事ではデジタルトランジスタのデータシートに記載されている用語についての解説と、各種パラメータを利用した設計計算方法について解説させていただきました。上記のパラメータはデジタルトランジスタの設計時に確認すべきパラメータになりますので、ぜひ設計にお役立てください