以下は「DCコイル(リレー/ソレノイド等)の逆起電力をダイオード+ツェナー(TVS含む)で吸収」するための実務レベル設計手順です。一次情報(メーカー資料・規格原文)に基づき、計算式・サンプル計算・部品選定・検証までをひと通り示します。

0. 文脈と前提(整理)

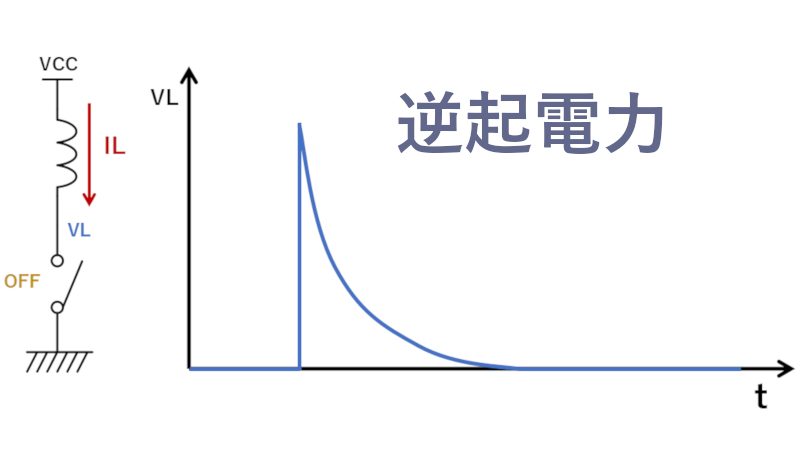

- 対象:DC駆動のリレー/ソレノイド等のインダクティブ負荷を、トランジスタ(BJT/MOSFET)でローサイドスイッチする一般的回路。

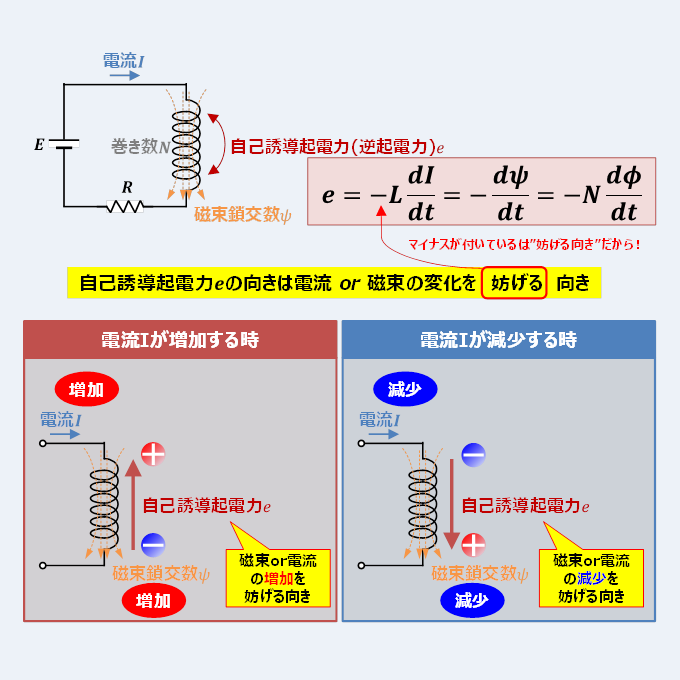

- 目的:**逆起電力(L di/dt)**を安全にクランプし、ドライバ素子の過電圧破壊とノイズ悪化を防ぐ。

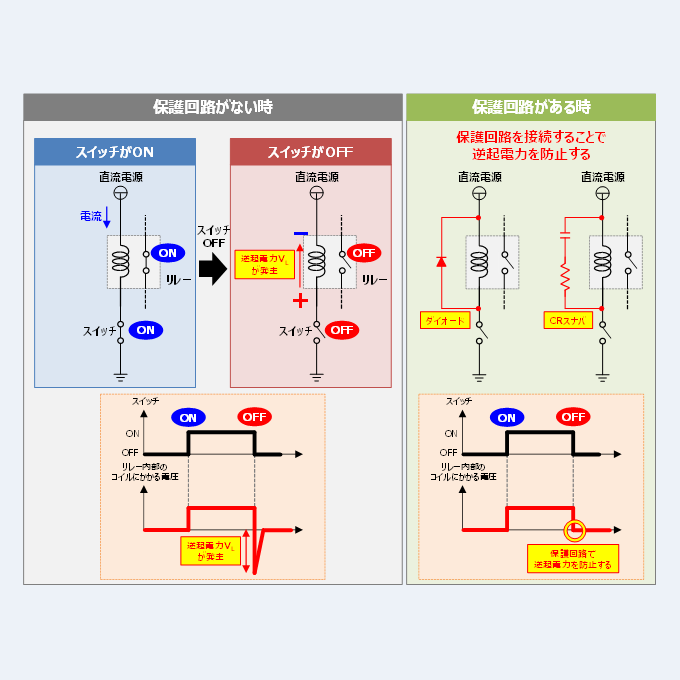

- クランプ方式:(A)フリーホイールダイオードのみ、(B)ダイオード直列ツェナー(Zener/TVS)、(C)TVS単体。本回答は**(B)を主対象**とし、必要に応じて(C)も併記。

- 重要トレードオフ:

- 開放時の減衰時間(速さ)⇔クランプ電圧(高いほど速い)

- 素子ストレス(ピーク電力/温度)⇔パルス幅/繰返し

- 騒音/EMI⇔電圧・電流の立上り/立下り

- 一次情報(代表例)

- TE Connectivity「Relay coil suppression」(TEコネクティビティ)

- TI「Using Motor Drivers to Drive Solenoids」(アクティブクランプの考え方)(Texas Instruments)

- TI「How to select a Surge Diode」(IEC 61000-4-5準拠のTVS選定指針)(Texas Instruments)

- Vishay「Typical TVS Applications」(リレーコイルへのTVS適用例)(vishay.com)

- onsemi アプリケーションノート(ツェナー/TVSのクランプ事例)(onsemi)

① 全体像(ブロック/信号フロー)

- 構成:DC電源 → コイル(L, R)→ ドライバTr(ローサイド)

- 抑制回路:コイル両端に「整流ダイオード+ツェナー」の直列を逆極性で接続

- 通電中:ダイオードが遮断、ツェナーも不導通 → 影響なし

- 断ト時:コイル電流が流れ続けようとし極性反転 → ダイオード順方向+ツェナー逆方向でV≈V_Z+V_F にクランプ → 電流を短時間で減衰

- ドライバが受ける最大電圧:V_SUPPLY + V_Z + V_F(ローサイドの場合)→ 素子の V_DS(max)/V_CE(max) との整合要

参考の抑制方式比較(一次情報での要旨)

- フリーホイールのみ:クランプ≈V_F → 減衰遅い(吸着遅れ・接点アーク増加の恐れ)(TEコネクティビティ)

- ダイオード+Zener/TVS:クランプ高 → 減衰速い(応答性/接点寿命に有利)(TEコネクティビティ)

- TVS単体:実装簡単・定格豊富(IEC61000-4-5等も視野)(Texas Instruments)

② 設計方針(優先順位とトレードオフ)

- ドライバの絶対最大定格保護(最優先):

V_SUPPLY + V_Z + V_F ≤ **0.8×**V_DRIVER_MAX(安全率例)。 - ターンオフ時間(t_off)の短縮:

t_off ≈ L·I_0 / V_CLAMP。高いV_CLAMPほど速く減衰。 - **素子ストレス(ピーク電力/温度)**を許容内に:

P_PK ≈ V_CLAMP·I_0、E_PULSE = ½·L·I_0²(エネルギはほぼツェナー/TVSが受け持つ)。 - EMI低減:必要ならライン側にRCスナバや追加の配線最適化を併用(配線ループ縮小等)。

- 量産性:温度/ばらつき/供給継続性(AEC-Q101等)を考慮。

③ 必要パラメータ一覧(記号・名称・単位・出典)

- ( V_{\text{SUPPLY}} )(V):コイル駆動電源電圧

- ( R_{\text{COIL}} )(Ω):コイル抵抗(データシート)

- ( L )(H):コイルインダクタンス(データシート or 実測)

- ( I_0 = V_{\text{SUPPLY}}/R_{\text{COIL}} )(A):通電直前のコイル電流(定常近似)

- ( V_{\text{Z}} )(V):ツェナー/TVSのクランプ電圧(I-V特性はデータシートで確認)

- ( V_{\text{F}} )(V):整流ダイオード順方向電圧

- ( V_{\text{CLAMP}} \approx V_{\text{Z}} + V_{\text{F}} )(V):コイルに印加されるクランプ電圧

- ドライバの最大許容電圧 ( V_{\text{DRV,max}} )(V):MOSFET V_DS(max)やBJT V_CE(max)

- 繰返し周波数 ( f_{\text{sw}} )(Hz):コイルON/OFF頻度

- 周囲温度範囲 ( T_A )(°C)・熱抵抗・パルスディレーティング曲線:素子データシート(TI/onsemi/Vishay/Nexperia 等)(Texas Instruments)

④ 設計手順(数式と適用範囲)

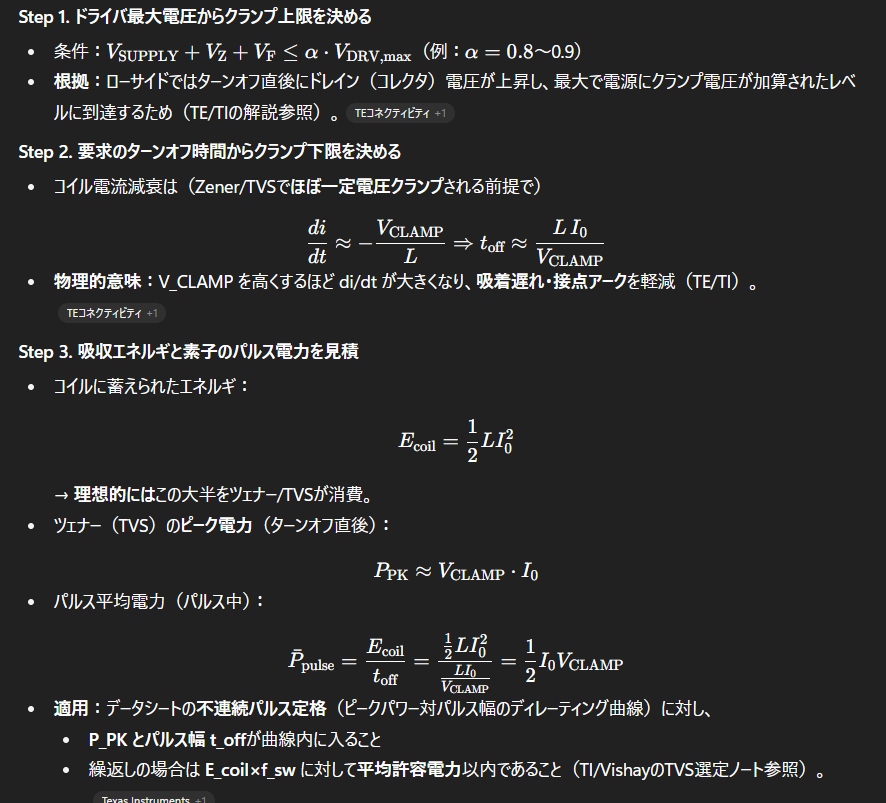

Step 1. ドライバ最大電圧からクランプ上限を決める

- 条件:( V_{\text{SUPPLY}} + V_{\text{Z}} + V_{\text{F}} \le \alpha \cdot V_{\text{DRV,max}} )(例:(\alpha=0.8)〜0.9)

- 根拠:ローサイドではターンオフ直後にドレイン(コレクタ)電圧が上昇し、最大で電源にクランプ電圧が加算されたレベルに到達するため(TE/TIの解説参照)。(TEコネクティビティ)

Step 2. 要求のターンオフ時間からクランプ下限を決める

- コイル電流減衰は(Zener/TVSでほぼ一定電圧クランプされる前提で)

[

\frac{di}{dt} \approx -\frac{V_{\text{CLAMP}}}{L} \Rightarrow

t_{\text{off}} \approx \frac{L,I_0}{V_{\text{CLAMP}}}

] - 物理的意味:V_CLAMP を高くするほど di/dt が大きくなり、吸着遅れ・接点アークを軽減(TE/TI)。(TEコネクティビティ)

Step 3. 吸収エネルギと素子のパルス電力を見積

- コイルに蓄えられたエネルギ:

[

E_{\text{coil}} = \frac{1}{2} L I_0^2

]

→ 理想的にはこの大半をツェナー/TVSが消費。 - ツェナー(TVS)のピーク電力(ターンオフ直後):

[

P_{\text{PK}} \approx V_{\text{CLAMP}} \cdot I_0

] - パルス平均電力(パルス中):

[

\bar{P}{\text{pulse}} = \frac{E{\text{coil}}}{t_{\text{off}}}

= \frac{\tfrac{1}{2}LI_0^2}{\frac{L I_0}{V_{\text{CLAMP}}}}

= \frac{1}{2} I_0 V_{\text{CLAMP}}

] - 適用:データシートの不連続パルス定格(ピークパワー対パルス幅のディレーティング曲線)に対し、

- P_PK とパルス幅 t_offが曲線内に入ること

- 繰返しの場合は E_coil×f_sw に対して平均許容電力以内であること(TI/VishayのTVS選定ノート参照)。(Texas Instruments)

Step 4. ツェナー/TVSの電圧・パッケージを選ぶ

- 電圧:Step1/2の範囲でできるだけ高めに設定(速い減衰)しつつ、ドライバ定格に十分余裕。

- 種別:繰返しパルス・エネルギが大きい場合は**サージ対応TVS(SMAJ/SMBJ/SMCJ/SMC)**が無難(Vishay/TI)。(vishay.com)

- 品質:産業/車載はAEC-Q101や高信頼グレードを優先(Nexperia/ Vishay 等)。(Nexperia)

Step 5. 直列ダイオードの選定

- 要件:初期電流 I_0をt_off流せるパルスIF、逆回復は厳しくないが信頼性重視でFRD/ショットキーが扱いやすい。IFSM(サージ)も確認。

- Vf は V_CLAMP に+されるため過度に高くしない。Vf 0.4〜1.0 V 程度が目安。

Step 6. 配置・配線

- クランプ素子はコイル端子直近に(最小ループでL di/dtのループ面積を抑える)—EMI低減(Vishay/TI)。(vishay.com)

Step 7. 温度・ばらつき・繰返しの確認

- 温度で V_Z, I-Vが変動(上昇/下降)→ 最悪条件で Step1 を再チェック。

- データシートのパルスディレーティング曲線で t_off(≒パルス幅)に対する余裕度を数値化(>2倍など)。

⑤ サンプル計算(すべて単位付・有効桁表示)

仮定(合理的):

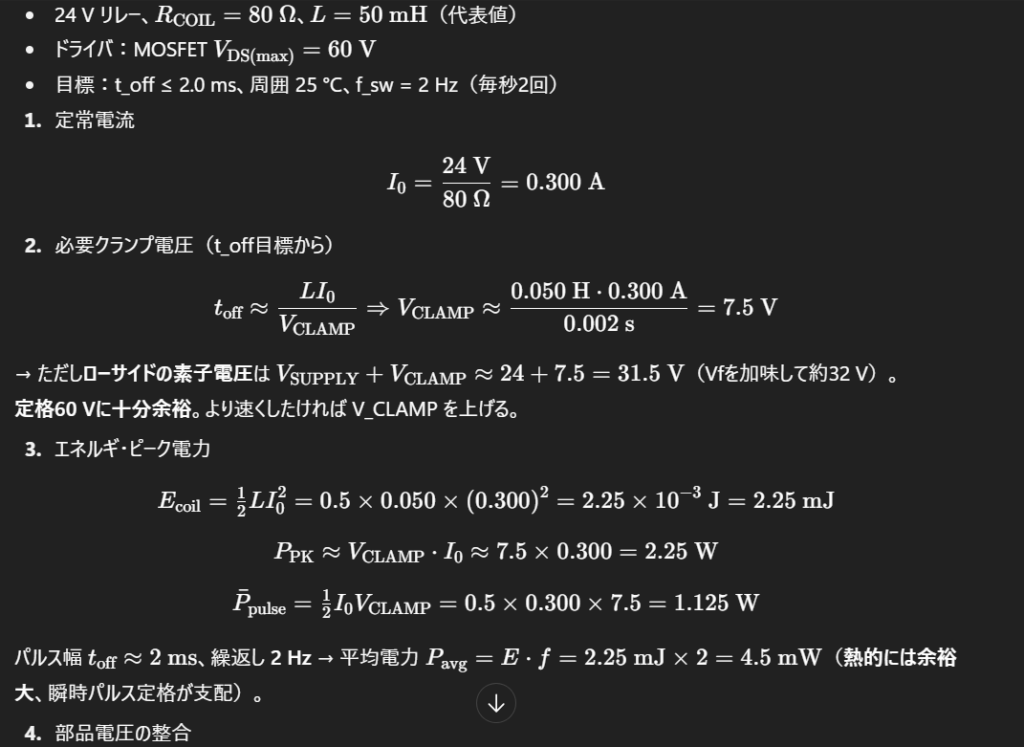

- 24 V リレー、( R_{\text{COIL}} = 80\ \Omega )、( L = 50\ \text{mH} )(代表値)

- ドライバ:MOSFET ( V_{\text{DS(max)}} = 60\ \text{V} )

- 目標:t_off ≤ 2.0 ms、周囲 25 °C、f_sw = 2 Hz(毎秒2回)

- 定常電流

[

I_0 = \frac{24\ \text{V}}{80\ \Omega} = 0.300\ \text{A}

] - 必要クランプ電圧(t_off目標から)

[

t_{\text{off}} \approx \frac{L I_0}{V_{\text{CLAMP}}} \Rightarrow

V_{\text{CLAMP}} \approx \frac{0.050\ \text{H} \cdot 0.300\ \text{A}}{0.002\ \text{s}}

= 7.5\ \text{V}

]

→ ただしローサイドの素子電圧は ( V_{\text{SUPPLY}} + V_{\text{CLAMP}} \approx 24 + 7.5 = 31.5\ \text{V} )(Vfを加味して約32 V)。

定格60 Vに十分余裕。より速くしたければ V_CLAMP を上げる。 - エネルギ・ピーク電力

[

E_{\text{coil}}=\tfrac12 L I_0^2

=0.5 \times 0.050 \times (0.300)^2

= 2.25 \times 10^{-3}\ \text{J} = 2.25\ \text{mJ}

]

[

P_{\text{PK}} \approx V_{\text{CLAMP}}\cdot I_0

\approx 7.5 \times 0.300 = 2.25\ \text{W}

]

[

\bar{P}{\text{pulse}} = \tfrac12 I_0 V{\text{CLAMP}}

=0.5 \times 0.300 \times 7.5 = 1.125\ \text{W}

]

パルス幅 (t_{\text{off}}\approx 2\ \text{ms})、繰返し 2 Hz → 平均電力 (P_{\text{avg}} = E \cdot f = 2.25\ \text{mJ}\times2=4.5\ \text{mW})(熱的には余裕大、瞬時パルス定格が支配)。 - 部品電圧の整合

- 例:SMBJ30A/SMBJ33A等のTVS(双方向/単方向)、またはツェナー 24–33 V クラスを候補。

- 実際の V_CLAMP はデータシートの**V_BR(@I_TEST)/V_C(@I_PULSE)**で決まる(Vishay/TI参照)。必要なら 12–24 V クラスに変更して t_off をさらに短縮可。(vishay.com)

- 直列ダイオード

- 初期電流 0.3 A、t≈2 ms → 1 A級FRD/ショットキーで十分(例:SMAパッケージ)。IFSMは数十Aが多く余裕。

※ 注意:より高速応答(t_offさらに短縮、接点アーク抑制)を狙うなら V_CLAMP を20–40 V程度に上げる設計も一般的(ただし MOSFET の V_DS マージン要)。この思想は TE/TI資料でも示唆。(TEコネクティビティ)

⑥ 公差設計(温度・経年・ラインばらつき・最悪条件)

- 温度:ツェナー/TVSの温度係数で V_Z が変動。**低温側でV_Z↑**する品種もある→ **V_SUPPLY + V_CLAMP(最大)**がドライバ定格を超えないことを確認。

- 供給電圧ばらつき:車載/産業では過電圧(例:バッテリ充電時)を想定 → **V_SUPPLY(max)**で再計算。

- L, R ばらつき:L↑やR↓で I_0↑ → E_coilとP_PKが増加。

- 繰返し・温度上昇:TVSのパルス対時間ディレーティング曲線にt_offと繰返しを当て、安全率≥2を確保(Vishay/TI)。(vishay.com)

⑦ 部品選定(候補と理由)

(代表例。最終は実回路の電圧/パルス条件で再選定)

- TVS/ツェナー

- Vishay SMBJ33A(33 V、SMBJ、広く入手・曲線整備)—TVS単体でのクランプにも適(リレー応用例あり)。(vishay.com)

- TIアプリノート準拠でサージ設計の指針が取りやすいデバイス群(SMAJ/SMBJ/SMCJ)(Texas Instruments)

- Nexperia TVS FlatPowerシリーズ(小型・高ピーク電力/AEC-Q101あり)—省実装高さに有利。(Nexperia)

- 整流ダイオード

- SS14(SMA, Schottky 1 A)/**UF4004(FRD 1 A)**クラス:I_0が小~中の一般用途に十分。

- 代替:Zener(BZX55/BZT52シリーズ)+整流ダイオード直列でも可。ただし繰返しパルスが大きい用途はTVS推奨(パルス定格が明確)。

⑧ 検証計画(シミュレーション/実測)

- SPICE:L, R, V_SUPPLY, ダイオード(Vf), TVS(V_BR・V_C・Cj)をモデル化。step paramで V_Z を掃引し t_off・P(t)=V·Iを評価。

- 実測:

- 高耐圧差動プローブ(> 100 V)でドライン(コレクタ)電圧波形、電流プローブでコイル電流波形。

- 記録する指標:V_CLAMP(最大), t_off, P_PK≈V_CLAMP·I_0, 素子表面温度(放熱が小さいSMA/SMBJはIR測温)。

- 配線ループ最小化・GNDリターン最短をレイアウトチェック(Vishay)。(vishay.com)

⑨ 信頼性・安全設計

- 熱:平均損失は小さくても繰返しピークで接合温度が上がる → メーカーの単発/繰返しパルス許容グラフで温度ディレーティングを確認(TI/Vishay)。(Texas Instruments)

- ストレス評価:

- 電圧:( V_{\text{SUPPLY(max)}} + V_{\text{CLAMP(max)}} ) < ( V_{\text{DRV,max}}/S_f )(例 S_f=1.25)

- エネルギ:( E_{\text{coil(max)}} ) を TVS のパルス定格曲線に対し余裕度≥2

- 簡易FMEA(抜粋)

- TVS短絡 → 常時電源過負荷(ヒューズ/ポリスイッチ推奨)

- TVS開放 → クランプ不能でドライバ破壊(過電圧モニタ/設計余裕)

- ダイオード逆実装 → 通電不能または常時クランプ(実装DFM・極性シルク)

⑩ 規格適合ポイント(該当条項・試験)

- ノイズ耐量を規格で評価する場合:

- 産業機器のサージ:IEC 61000-4-5(波形・レベル・源インピーダンス規定、TVS選定の考え方に対応)(Texas Instruments)

- 車載の車載ライン擾乱:ISO 7637(車載電源ラインの擾乱—TVSやクランプで対策)(vishay.com)

- リレー応用:TEアプリノート(接点寿命/抑制素子の影響の考察)(TEコネクティビティ)

※コイル自体の逆起電力対策は上記の系規格適合の一構成要素。実機では電源ライン側のサージ/ESDも別途評価。

⑪ よくある落とし穴(回避策)

- クランプ電圧を低くしすぎる(フリーホイール相当):t_off が長く接点アーク/粘り/他回路遅延が悪化 → Zener/TVSで適度に高い V_CLAMPへ。(TEコネクティビティ)

- ドライバ定格オーバ:V_SUPPLY上振れ+温度でV_Z↑を見落とし → 最悪条件で V_DS/V_CE マージンを確保。

- TVSのパルス曲線未確認:E, t_off, 繰返しを曲線に当てていない → ディレーティング曲線に必ず当て込む(TI/Vishay)。(Texas Instruments)

- 配線ループが大きい:EMI/オーバシュート増大 → コイル端子直近に配置、リターン最短。

- 実装極性ミス:シルク・回路図表記・実装手順をDFMで固める。

⑫ 参考文献(一次情報中心・URL付)

- TE Connectivity, Relay coil suppression(DC relays):リレー接点寿命と抑制方式の影響。(TEコネクティビティ)

- Texas Instruments, Using Motor Drivers to Drive Solenoids(SLVAE59):クランプで減衰を速める考え方と波形。(Texas Instruments)

- Texas Instruments, How to select a Surge Diode(SLVAE37):IEC 61000-4-5に基づくTVS選定。(Texas Instruments)

- Vishay, Typical TVS Applications:リレーコイルのTVS適用例・配線の要点。(vishay.com)

- onsemi, アプリケーションノート(例 AND8116/他):リレーのコイルスパイクをツェナーで抑制する事例。(onsemi)

- Nexperia, Transient Voltage Suppressors(製品ポートフォリオ/AEC-Q101):高ピーク電力・薄型実装。(Nexperia)

要約(実装のコア)

- V_CLAMP の許容範囲=「速く落としたい最小値」〜「ドライバ定格で許される最大値」。

- ( t_{\text{off}}\approx L I_0/V_{\text{CLAMP}} )、( E=\tfrac12 L I_0^2 )、( P_{\text{PK}}\approx V_{\text{CLAMP}}I_0 )。

- TVS/ツェナーはパルス定格曲線に当て、P_PK・t_off・繰返しで余裕度≥2。

- 配線は最短・コイル直近、極性ミス防止。

- 必要に応じてTVS単体やRCスナバを併用してEMI最適化。

補足:TVS単体の採用基準(簡易)

- 供給ラインのサージ(IEC 61000-4-5)も視野に入れる場合、TVS単体でライン対GNDに入れた方が系として整理が簡単。クランプ電圧はドライバ定格と装置規格の両立点で決定(TI/Vishay)。(Texas Instruments)

もし具体のコイル仕様(R, L, I_0, V_DS(max), 繰返し)をご提示いただければ、V_Z候補(数値)→TVS型番→t_off 実測想定値まで落とし込みます

。

非常に鋭い質問です。

はい、短時間で繰り返し瞬時短絡が発生すると、ダイオードは急速に劣化し、最終的に破壊に至る可能性が高くなります。

この現象は「繰返しパルスストレス(repetitive surge stress)」として定義されており、整流ダイオード/ショットキーダイオード/TVSツェナーすべてに共通して重要です。

以下で、破壊メカニズム → 熱的過程 → 定格評価 → 実務対策を順に詳しく説明します。

① 繰返し短絡とは何が起きているか

ダイオードが逆向き実装や短絡状態にある場合、

通電ONのたびに電源から**大電流(IF, surge)**が流れます。

このときの瞬時電流は次式で近似できます:

I_{\text{surge}} = \frac{V_{\text{supply}} – V_F}{R_{\text{line}} + R_{\text{coil}}}

仮に 24 V 系でライン抵抗が 1 Ω 以下なら、

→ 20 A〜50 A級のパルス電流が瞬時に流れます(ms以下)。

これが何度も繰り返されると、接合温度が急上昇・冷却の繰返しを受けてダイオードが疲労・破壊します。

② 破壊メカニズム(物理的に何が起きているか)

| 種別 | 現象 | 説明 |

| ① 熱破壊(thermal runaway) | パルス電流による瞬間発熱 → ジャンクション温度 Tj が絶対最大 (Tjmax≈150〜175 °C) を超過 | ショート直後はパルス幅が短くても、繰返すと蓄熱で破壊 |

| ② メタル疲労/ワイヤボンディング断線 | 繰返し通電で内部ワイヤが加熱膨張→冷却収縮を繰返す | 接合部クラック・抵抗増加・最終的にオープン故障 |

| ③ エピ層溶融/シリコン局所焼損 | 大電流集中で局所温度1000 °C超、結晶溶解 | 黒化・リーク増加・永久短絡(破壊) |

| ④ パッケージ損傷 | リードフレームと樹脂界面の熱膨張差で剥離 | 外観異常なく内部断線 |

③ ダイオードの定格で見る「繰返し短絡の危険性」

メーカーのデータシートでは以下のような定格があります。

| 項目 | 意味 | 対応する危険 |

| IFSM(非繰返しサージ電流) | 単発の大電流に耐えられる限界(例:50 A/10 ms) | 「一度だけ」ならOKだが、繰返しはNG |

| IFRM(繰返しピーク順方向電流) | 定常的に許されるパルス電流(例:1 A @ 50% duty) | 「周期的に短絡が発生」する場合はこれを超える |

| ΔTj/pulse(温度上昇パルス許容) | パルスごとの温度上昇 | 周期短すぎると冷却が追いつかず破壊 |

たとえば Vishay「SS14(1 Aショットキー)」の場合:

- IFSM ≈ 30 A (8.3 ms, single half-sine)

- しかし「repetitive surge」は保証外。数回で寿命急減。

つまり、瞬時短絡が何度も発生する=

「IFSMを繰返す」状態であり、破壊リスクが極めて高いです。

④ 熱的観点での定量評価(概算)

パルスによる瞬間発熱エネルギー:

E_{\text{pulse}} = I_{\text{surge}}^2 \cdot R_{\text{j}} \cdot t_{\text{pulse}}

ダイオードの熱抵抗を RθJA=100 K/W、Isurge=30 A、t=2 ms、Rj=0.1 Ω と仮定すると:

E = 30^2 \times 0.1 \times 0.002 = 0.18\ \text{J}

温度上昇:

ΔT = \frac{E}{C_{\text{th}}}

Cth(熱容量)≈0.1 J/K の場合、

ΔT ≈ 1.8 K/1パルス。→ 1 Hz で繰返すと蓄熱し Tj上昇が積み重なる。

100パルス程度で内部クラックや抵抗増加が発生しうる。

⑤ 実務でよく起きるパターン

| 状況 | 現象 | 結果 |

| リレー駆動でダイオード逆実装 | 通電時に瞬時短絡(30 Aクラス)を毎回発生 | 数十回でダイオード短絡化・焼損 |

| コイルのPWM制御で逆接 | 数kHzパルスごとに短絡 → ダイオード過熱 | 数秒で破壊(煙発生) |

| スイッチング電源で整流側逆極性 | 起動時突入が繰返し | 整流素子溶損・FET破壊連鎖 |

⑥ 実務上の防止策

| 対策 | 目的 | 備考 |

| 1. フェイルセーフ設計 | 逆接時でも短絡電流を制限 | ヒューズ、PTC、電源抵抗を直列に挿入 |

| 2. 逆接ダイオードを別途追加 | 保護方向を限定 | 電源ラインに逆接保護用ダイオードを追加 |

| 3. 実装検査 | 極性誤実装を防止 | カソードマーク明記・AOIで検査 |

| 4. サージ・繰返し耐量の余裕 | 繰返し負荷でも安全 | 定格 IFSM の3〜5倍の余裕を持つ大型素子採用 |

| 5. 熱シミュレーション・実測 | 温度上昇評価 | 熱画像/IRセンサでΔTパルス確認 |

⑦ メーカー資料での裏付け(一次情報)

- Vishay General Semiconductor – “AN-1005: Diodes and Surge Current”

「繰返しサージは非推奨。IFSMは単発条件でのみ有効」と明記。

“Repetitive surges, even below IFSM, cause cumulative damage due to thermal cycling.” - ON Semiconductor – “Thermal considerations for Power Diodes”

「短時間サージを繰返すとボンディング部が疲労破壊する」と記載。

“Repeated surge events accelerate metallurgical fatigue of bond wires.”

⑧ 結論

短時間で瞬時短絡が繰り返されると、ダイオード破壊リスクは急激に上がる。

原因:

- 大電流 → 熱衝撃 → 熱疲労・接合劣化の蓄積。

- 「IFSM」はあくまで単発保証であり、繰返しは不可。

結果:

- 初期は通電可能でもリーク増大→VF上昇→最終的に短絡または開放。

- 実際には数十回の短絡で破壊することが多い(SMA/SMBJ級では特に)。

⑨ 実務アドバイス(簡潔まとめ)

| 現象 | 評価指標 | 許容指針 |

| 単発短絡(誤接瞬間1回) | IFSM以下 | 一般に耐える |

| 数回/秒オーダの繰返し | IFRM超過 | 数十回で破壊可能 |

| 数百Hz以上で繰返し | 熱蓄積で即破壊 | 1秒以内に破損もあり |

最終結論:

ダイオードに瞬時短絡(大電流パルス)が繰返し印加されると、

- 内部の熱応力疲労、

- ボンディング断線、

- 接合溶融、

のいずれかにより数回〜数十回で破壊する可能性が極めて高いです。

したがって、「一度でも短絡が起きる回路」では原因除去が最優先であり、

素子のサージ定格に頼ってはいけません。

希望があれば、次に

✅「繰返し短絡を想定した熱破壊シミュレーション方法(I²t換算とサージエネルギ)」

✅「破壊防止用の保護ヒューズ/NTC設計手順」

を数式付きで解説できます。進めますか?